|

Pentagon by Northwood

|

|

| Black_Cat | Дата: Среда, 01.07.2020, 16:12 | Сообщение # 1 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

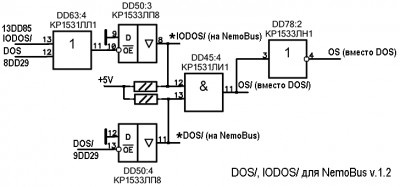

| 1. Сигналы DOS/, IODOS/ для NemoBus v.1.2

Цепи DOS/, DOS на выходе DD29 идущие на дешифрацию портов разорвать, и в разрыв врезать схему. Цепи, идущие на выборку ПЗУ оставить как есть.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Пятница, 18.09.2020, 16:59 | Сообщение # 181 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) Не мог бы ты прояснить чо у тебя там наворочено с Глюком. В моём понимании, для работы с Глюком достаточно одного тумблера - загрузка по RST0 из Глюка, или из SOS128. ВСЁ! У тя же там чото наворочено с триггерами, мультиплексорами и логикой на несколько корпусов.

Чтобы решить эту проблему и сделать возможным из ОЗУ перейти в Глюк, служит дополнительный триггер, который стоит первым в схеме.

Первый триггер в исходном состоянии удерживает сброс второго триггера до тех пор, пока не будет выполнен переход из ОЗУ в ПЗУ. Это обеспечивает доступ к ПЗУ Глюк после ОЗУ. Как только переход в ПЗУ состоялся, первый триггер переключается и отпускает сброс 2-го триггера, который всё ещё остаётся в сброшенном состоянии, что обеспечивает эту же страницу ПЗУ Глюк. Далее стандартно в самом Глюке код начинает выполняться ОЗУ, что переключает второй триггер и это отключает страницу ПЗУ Глюк.

В ПЗУ BIOS происходит тестирование доступности всех 4-х страниц ПЗУ, поэтому требуется возможность в любой момент достучаться в ПЗУ Глюк после любой другой страницы ПЗУ. Для этого я ввёл сброс триггера Глюк через порт BIOS #FF37. Активировав кратковременно сигнал RESGLK оба триггера возвращаются в исходное состояние.

Я могу даже из STS 3.3 пройтись по ПЗУ Глюк с 0-го адреса, если не снимать сброс триггеров Глюк.

Добавлено (18.09.2020, 17:07)

---------------------------------------------

Мультиплексор нужен для других целей - для переключения режимов коммутации страниц ПЗУ:

0) - стандартный режим - Порт #7FFD D4, триггер TR-DOS, триггер Глюк;

1) - режим +3 - Порт #7FFD D4, Порт #1FFD D2;

2) - режим программирования ПЗУ - Порт #7FFD D4, Порт #1FFD D2.

В режиме программирования ПЗУ я решил не изобретать велосипед, а использовал такой же принцип переключения всех 4-х страниц ПЗУ, как в режиме +3, т.е. использую облегчённый доступ ко всем 4-м страницам ПЗУ.

Добавлено (18.09.2020, 17:41)

---------------------------------------------

И между режимами программирования ПЗУ и +3 есть одно ключевое отличие: Режим +3 включает старшие 4 страницы ПЗУ, выключенный данный режим включает нижние 4 страницы ПЗУ, т.е. управляет A16 ПЗУ. А режим программирования ПЗУ состояние А16 не изменяет. Поэтому во время программирования ПЗУ, для выбора любой из 8 страниц ПЗУ, необходимо управляться #7FFD D4,.#1FFD D2 и режимом +3 через порт #FC37 D5.

Сообщение отредактировал Northwood - Пятница, 18.09.2020, 18:28 |

| |

|

|

| Northwood | Дата: Воскресенье, 20.09.2020, 16:39 | Сообщение # 182 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Забыл про A2 в дешифраторе портов BIOS #xx37 для исключения конфликта с портом #33. Добавил на схему, доразвёл это на плате.

Ревизия материнки теперь 8.3.

Сообщение отредактировал Northwood - Воскресенье, 20.09.2020, 16:39 |

| |

|

|

| Black_Cat | Дата: Воскресенье, 20.09.2020, 17:35 | Сообщение # 183 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| Вот такой вот шкурный вопрос: а для DD33 настолько критично нужна КР1531КП19, шо низзя заюзать КП12 с доп инвертором?

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Воскресенье, 20.09.2020, 18:45 | Сообщение # 184 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) Вот такой вот шкурный вопрос: а для DD33 настолько критично нужна КР1531КП19, шо низзя заюзать КП12 с доп инвертором?

Не на КП12, а на КП2, потому что при отключении выхода КП2 уровень должен стать 0, а после инвертора 1.

А чем вызвано желание такой замены ? КП19 разве сложно достать ? Тянуть 2 длинные дорожки до ближайшего инвертора DD54:2 будет сложно.

Сообщение отредактировал Northwood - Воскресенье, 20.09.2020, 18:46 |

| |

|

|

| Black_Cat | Дата: Воскресенье, 20.09.2020, 19:26 | Сообщение # 185 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| Цитата Northwood (  ) Не на КП12, а на КП2, потому что при отключении выхода КП2 уровень должен стать 0, а после инвертора 1.

:) Прелесть Z- состояния в том, что выход в таком состоянии можно притянуть резистором как к питанию, так и к нулю :) . Ставим КП12 с пуллдауном на выходе и инвертором. и не надо ни КП2 ни КП19 :) . Профит в увеличении унификации комплектухи, и во втором мультиплексоре, который не пропадает, и который можно задействовать как ЛП8.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Воскресенье, 20.09.2020, 20:19 | Сообщение # 186 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Не вижу смысла. Ставим КП19 и не надо ничего придумывать с инвертором. ЛП8 и так остался один лишний элемент.

|

| |

|

|

| Black_Cat | Дата: Понедельник, 21.09.2020, 22:16 | Сообщение # 187 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| Вопрос: у тя в ловушке данные кода защёлкиваются по переднему фронту, в то время как они валидны токо по заднему.. Это как вааще?

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Понедельник, 21.09.2020, 23:24 | Сообщение # 188 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) Вопрос: у тя в ловушке данные кода защёлкиваются по переднему фронту, в то время как они валидны токо по заднему.. Это как вааще?

Проверено - работает. "Insult Megademo" включая скрытую часть, а так же STS 3.3, работают без проблем.

|

| |

|

|

| Black_Cat | Дата: Вторник, 22.09.2020, 12:30 | Сообщение # 189 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| А почему было не включить штатно по заднему фронту? И кстати, я подрихтовал адаптер под divIDE, +1 корпус :) . А чо светодиод не добавил? Народу нравится поморгать светодиодом из бейсика, а можно ведь ещё индикацию блокировки сделать :) . Да и джампер не помешал бы, вдруг этот адаптер захотят воткнуть в комп без BDI, например в KAY, а на divIDE хоть кривоватая, но какая-то эмуляция BDI есть :) .

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Вторник, 22.09.2020, 23:15 | Сообщение # 190 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Временная диаграмма сигналов видеоконтроллера - счётчиков, строчных и кадровых гасящих и синхроимпульсов, а так же начала сигнала INT.

|

| |

|

|

| Black_Cat | Дата: Среда, 23.09.2020, 15:35 | Сообщение # 191 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| Токо обратил внимание, шо верхняя и нижняя платы не могут быть воткнуты непосредственно друг в друга, а требуется переходник, судя по всему - плоский кабель. Очень плохое решение. Что плоский кабель не подходит для подключения периферии убедились все, кто имел дело с нэдописишными турбосаундами, в которых приходилось экспериментально укорачивать кабель шоб добиться безсбойной работы. Лучче уж поставить верхнюю плату вертикально, шоб она втыкалась в IDC разъём на мамке, а разъёмы поменять на впаивающиеся прямо в верхнюю платуперпендикулярно, а угловые. В этом случае верхняя плата так же будет выполнять роль заглушки в заднице компа.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Среда, 23.09.2020, 21:34 | Сообщение # 192 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) Вопрос: у тя в ловушке данные кода защёлкиваются по переднему фронту, в то время как они валидны токо по заднему.. Это как вааще?

Посмотрел схему доработок Пентагона-1024 1.4, которую я делал, там у меня всё-таки сделано по заднему фронту, поскольку М1/ я подал прямо на тактовый вход ТМ2, без MREQ/. Так что ты прав, буду исправлять.

|

| |

|

|

| Black_Cat | Дата: Четверг, 24.09.2020, 18:13 | Сообщение # 193 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| А в чом смысл сдвига инта XJ5 ?

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Четверг, 24.09.2020, 18:47 | Сообщение # 194 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) А в чом смысл сдвига инта XJ5 ?

В том, что я не уверен, в каком из двух положений джампера положение INT будет точно таким как надо. Чтобы потом дорожки не резать, а просто переключить джампер так, чтобы бордюрные эффекты под Пентагон-128 полностью сошлись.

P.s. исправил ловушку, теперь она срабатывает по заднему фронту, как положено.

|

| |

|

|

| Northwood | Дата: Четверг, 24.09.2020, 23:21 | Сообщение # 195 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Дополнил временную диаграмму сигналом Border.

|

| |

|

|

| Northwood | Дата: Пятница, 25.09.2020, 09:29 | Сообщение # 196 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) око обратил внимание, шо верхняя и нижняя платы не могут быть воткнуты непосредственно друг в друга, а требуется переходник, судя по всему - плоский кабель.

Да, требуется шлейф, но длиной максимум 10 см.

Цитата Black_Cat (  ) Очень плохое решение. Что плоский кабель не подходит для подключения периферии убедились все, кто имел дело с нэдописишными турбосаундами, в которых приходилось экспериментально укорачивать кабель шоб добиться безсбойной работы.

Я не знаю, с какой длины до какой укорачивали люди шлейфы, но у меня NedoPC-шный TurboSound-FM работает без никаких сбоев со шлейфом длиной около 12 см, точно не измерял, при этом в режиме Турбо-7 МГц без WAIT-а портов:

Для верхней платы можно будет использовать более короткий шлейф.

Цитата Black_Cat (  ) Лучче уж поставить верхнюю плату вертикально, шоб она втыкалась в IDC разъём на мамке, а разъёмы поменять на впаивающиеся прямо в верхнюю платуперпендикулярно, а угловые. В этом случае верхняя плата так же будет выполнять роль заглушки в заднице компа.

Не понял на счёт "а угловые", может наоборот, разъёмы должны быть не угловые ? Или ты имел ввиду разъём, который будет соединять верхнюю плату с материнкой ? Тот да, должен быть угловой.

Но идея хорошая, верхнюю плату можно будет механически закрепить латунными стоечками к задней стенке корпуса вместо куллера, который не нужен. Если только размеры платы не превышают лимит, накладываемый глубиной корпуса ATX.

Добавлено (25.09.2020, 09:42)

---------------------------------------------

Только одна проблема - прямой разъём PS/2 я наверно не найду.

Сообщение отредактировал Northwood - Пятница, 25.09.2020, 10:18 |

| |

|

|

| Black_Cat | Дата: Суббота, 26.09.2020, 11:08 | Сообщение # 197 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| 15. Комплексные доработки и исправления дешифраторов, менеджеров памяти и АВМ.

К сожалению, тот способ маскирования, что сделан у тебя, концептуально ошибочен ввиду того, что внешнее устройство имеет возможность перебить установки компа и залезть в память, куда ему доступа не должно быть. Поэтому придёцца не костылить, как пытался ты, а всё делать по фэньшую :) , что изрядно добавит корпусов. Поэтому перед тем как добавить что-то ненужное, надо сначала выкинуть что-то ненужное :) , чем мы и займёмся, упрощая схемотехнику, и попутно устраняя баги :). Итак, смотрим простыню картинки, и движемся по номерам:

1)2)Устраняем дублирование BLK14|15/, и заодно меняем ЛА4 на ЛИ3, меняя местами выходы D41.1 и заменив ЛИ на ЛЕ в схеме 3).

4) Меняем ЛЕ на ЛН.

5) Входы с шины принципиально не могут идти на диоды, т.к. внешние устройства имеют полное право эмулиовать ОК с помощью диода, а два последовательных диода уже превышают ТТЛ уровень нуля. Меняем диоды на ЛИ.

6) Выбрасываем лишнюю ЛИ1 в формирователе NMI/, и добавляем диоды с выходов D70.4 и АГ3 на NMI/. Стоявший вместо диода резистор выкидываем, т.к. уже есть пуллап.

7) Меняем инверторы на ЛЕ.

8) Неправильная полярность строба защёлки, меняем ЛЕ на ЛЛ+ЛН. Делаем более правильную блокировку #xxFD.

9)10)11) Делаем более быструю и более правильную дешифрацию портов #xxFD, замешивая IORQG, RD, WR в конце, и при этом ещё экономим несколько корпусов. Кроме того исправляем ошибку, когда вейт генерился так же при обращении к #DFFD, а не только к AY.

12) Из сэкономленных элементов делаем экономичный безконфликтный дешифратор для периферии.

13) Делаем раздельную дешифрацию #FE на RD/WR для устранения возможности конфликта чтения клавиатуры и портов #xxFD при чтении например из #FC. Таких адресов, обратившись к которым можно спалить железо, быть не должно принципиально!

14) Делаем более правильную дешифрацию Кемпстон джойстика и по #DF и по #1F. Заодно устраняем конфликт с портами NemoIDE.

15) Аналогично, для мыши делаем шоб она откликалась токо на in a,©, и не реагировала на джой.

16) Замешиваем IOWR/ в конце, убыстряя дешифрацию и отделяя сигнал защёлки чипселекта #7FFD.

17) Замешиваем IOWR/ в конце, убыстряя дешифрацию и делаем шоб запись в #7FFD блокировалась по всем разрядам. Для этого компа это не имеет значения, но исторически, наверно, это более правильно, т.к. при самопальном расширении доп разряды подключались именно к чипселекту ТМ9.

18) Замешиваем IOWR/ в конце, убыстряя дешифрацию и делаем правильную блокировку D5. Маскирование D6 убираем, т.к. не соответствует концепции. Там же формируем сигнал KERNEL/.

19) Соответственно, меняем выборку мультиплексирования разрядов.

20) Меняем чтение из портов #xxFD.

21) Заменяем ЛИ1 на КП11.

22) Реализуем правильный способ доступа с шины - либо через полный захват шины по фэньшую, либо токо для мастер-слота занулением сигнала EXTERNAL ADRESS (EA\BUSAK/), который должен быть токо на мастер слоте, а на слейвах - токо BUSAK/. Соответственно, по этому сигналу мультиплексоры отключаются от шины, и внешнее устройство может подать туда сигнал со своего менеджера памяти. Но!!! Преодолеть ограничения, заданные маской и адресом текущей АВМ внешнее устройство не сможет, а сможет токо управлять памятью в рамках текущей АВМ. Для этого адресные линии менеджера памяти выводим на шину не после резисторов, а до них!

23) Замешиваем IOWR/IORD в конце, убыстряя дешифратор.

24) На сэкономленные элементы добавляем ИД4 для доп. портов маски #6DF7 и адреса #6FF7 АВМ. От порта #EFF7 берём токо половину разрядов, которые будут так же доступны по #EDF7, и считать их можно будет тоже только по #EDF7(точнее - это официальный порт, хотя считать можно по нескольким адресам).

25) Т.к. мы для убыстрения дешифрации повыкидывали IORQG/, то этот сигнал надо добавить в формирователь вейта, что и делаем с помощью пары диодов и инвертора.

26) В дешифраторе #7B/#FB меняем ЛЕ1 на ЛЛ1, и используем сигнал xB/.

27) Для работы с модемом юзаем сигнал EF/, при том подаём его так же на A4 ISA(A27) в качестве чипселекта, а на самом модеме перемычками выставляем COM3(#3E8), IRQ4. Соответственно на ISA подаём непосредственно IORD/, IOWR/, экономя кучку элементов.

28) Для дешифрации порта атрибутов юзаем сигнал RFF/.

29) Для дешифрации портов #xx37 юзаем сигнал #x3, попутно устраняя конфликт всех этих портов с BDI.

30) Добавляем корпус ЛН2 и высвобождаем ЛП8.

31) Из сэкономленных элементов собираем самый быстрый арбитр шины на 3 слота, запараллеливая два мастер-слота(которые ближе к краю платы).

32) Ну и наконец, заменив сэкономленные корпуса, и добавив корпус ЛП8, собираем такой менеджер АВМ, позволяющий устанавливать следующие ограничения адресного пространства АВМ: 16k(16k ПЗУ или 16k ОЗУ или их комбинации), 32k, 64k, 128k, 256k, 512k, 1Mb, 2Mb, 4Mb. Я решил не усложнять схему, выкусыванием 16k ОЗУ, находящихся под ПЗУ, т.к. маловероятна необходимость использования максимально возможного количества АВМ, и тем самым породил два варианта использования АВМ 32k и 64k - либо как стандартные Spectrum 16k/48k с потерей ОЗУ под ПЗУ, либо как некие мутанты Spectrum 32k/64k, с дополнительным экраном в странице RAM0, переключаемым #7FFD. А в Spectrum 32k до RAM0 можно добраться токо отключив ПЗУ, или другими способами, которые пока ещё на этой плате не реализованы :) . По сбросу, автоматически выставляется маска #80. При записи маски #00, старший разряд маски формирует сигнал AllRAM/. Разрешёнными являются только такие значения маски: 16k/#FF, 32k/#FE, 64k/#FC, 128k/#F8, 256k/#F0, 512k/#E0, 1Mb/#C0, 2Mb/#80, 4Mb/#00. В качестве регистра адреса АВМ используем DD12, удалив #FC37, и перекинув лишние сигналы на другие порты #xx37.

33) На верхней плате выкидываем корпус ИД7 и изменяем дешифратор.

P.S. Внизу картинки сэкономленные и текущие свободные элементы. Т.к. ты модифицируя схему постоянно менял нумерацию микросхем, то нумерация привязана к довольно старому варианту в аттаче:

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Суббота, 26.09.2020, 15:29 | Сообщение # 198 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Разбивать память для АВМ на куски по 16 КБ я не хочу. 128 КБ будет минимум.

Добавлено (26.09.2020, 15:31)

---------------------------------------------

Цитата Black_Cat (  ) что изрядно добавит корпусов

На плате корпуса добавлять уже некуда. Если в итоге получается хоть на 1 корпус больше чем сейчас, от всех этих доработок придётся отказаться.

Добавлено (26.09.2020, 17:21)

---------------------------------------------

У тебя во вложении в PDF давно устаревшая версия схемы, она давно не актуальна. Я же после той схемы, которую ты выложил в своём сообщении, ещё несколько раз выкладывал обновлённые схемы с теми или иными исправлениями.

Самая последняя моя версия была 8.4 в посте № 194. Я не знаю, от чего ты отталкивался, когда составлял список доработок.

Я пройдусь по каждому пункту твоих доработок и попробую применить у себя, но скорей всего не все приму. И посмотрю, что из этого получится. Сейчас моя последняя версия платы 8.4, она полностью разведена. Если из твоих доработок что-то войдёт, то это будет версия 9.0.

Сообщение отредактировал Northwood - Суббота, 26.09.2020, 17:25 |

| |

|

|

| Black_Cat | Дата: Суббота, 26.09.2020, 17:24 | Сообщение # 199 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| Цитата Northwood (  ) На плате корпуса добавлять уже некуда. Если в итоге получается хоть на 1 корпус больше чем сейчас, от всех этих доработок придётся отказаться.

Ты не понял, всё делалось относительно старой схемы, где ты ещё не начал добавлять микросхемы. И вот относительно этой старой схемы с меньшим чем у тебя сейчас количеством микросхем, на все эти изменения добавлен всего один корпус. Т.е. по идее схема должна получиться по корпусам меньше чем у тебя сейчас. Так что если сделать все эти изменения, то количество корпусов возможно даже уменьшится по сравнению с твоей последней ревизией. На мамке было сэкономлено 6 корпусов, а добавлено 7 (-6+7=+1), и 1 корпус сэкономлен на верхней плате. Конечно, это не окончательный вариант, а только где-то ближе к половине того пути, который нам ещё надо пройти до запуска в производство. Так что, если ты считал, что уже сидишь на чемоданах перед отправкой в производство, то ты ошибся - всё что мы уже прошли, плюс после добавления всех этих изменений - это будет токо половина того, что должно быть сделано :) .

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Northwood | Дата: Суббота, 26.09.2020, 21:31 | Сообщение # 200 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| 1, 2) я согласен с тем, что там получилось дублирование, но твой вариант изменений меня не устраивает. Не устраивает тем, что на запись в ПЗУ сигналы адреса A14 и A15 до линии SRWE/ проходят сразу 4 каскада. Это слишком много, к тому же в моей схеме они проходили только 3 каскада. Я сделал доработку по-своему, это добавило + 1 элемент "НЕ", который взял из оставшихся свободных, сигналы адреса теперь проходят всего 3 каскада.

1, 2) ты не учёл, что в последней версии схемы элемент DD47:4 (ЛА3) уже давно занят в формирователе сигналов NB_IODOS/, DOS и DOS/. Я могу вернуть туда элемент ЛЛ1, но тогда мне снова надо проинвертировать входной сигнал IODOS. Напомню ошибку твоего решения брать уже инвесрный сигнал IODOS/ с микросхемы часов. Она питается от литиевой батарейки, у которой ёмкость всего 250 мА/час, от неё же формируется инверсный сигнал IODOS/, который подаётся на вход CS/ микросхемы часов. Потребление от этой батарейки в единицах микро-ампер, поэтому если брать оттуда сигнал для микросхем логики, то это будет быстро высаживать батарейку через резистор R59. Поэтому я ещё давно внёс изменение в твою схему, заменив ЛЛ1 на ЛА3 DD47:4, чтобы брать неинверсный сигнал IODOS с порта #EFF7.

Добавлено (27.09.2020, 10:34)

---------------------------------------------

8) Полярность защёлки я исправил в ревизии 8.4.

8) Твоя схема блокировки xxFD не более правильная, а альтернативная, т.к. в моей схеме ошибок нет.

9)10)11) На счёт более быстрой схемы, очень и очень спорно. Например:

При обращении к AY через OUT (#FD),A у тебя максимальный путь прохождения значих адресных сигналов A14 и A15 составляет целых 6 каскадов, один из которых ИД7. У меня только 4 каскада, один из которых ИД7.

При обращении к порту #DFFD у тебя максимальный путь прохождения адресных сигналов составляет 4 каскада, один из которых ИД7. У меня только 2 каскада, один из которых ИД7.

Сомнительный прирост производительности.

При этом в твоей схеме есть грубая ошибка: Если при записи в порты AY логически всё хорошо, то при чтении у тебя IORQG/ вообще не заведён. Т.е. AY будет гадить на шину при чтении из ОЗУ в диапазоне адресов #8000-#FFFF, что приведёт к полной неработоспособности компьютера при установленном AY. Если завести забытый IORQG/ в конце, то количество каскадов логики увеличится до 7, против моих 4-х. Стало быть, его надо вернуть назад на DD58 как было.Добавлено (27.09.2020, 11:19)

---------------------------------------------

13) В моей схеме для достижения того же результата что и у тебя, достаточно просто заменить A6 на A1 и всё. Я не помню, почему я завёл A6 в дешифратор, но для разделения с NemoIDE и со SMUC действительно достаточно только A2, а больше других портов с чётными адресами я вспомнить не могу. Т.е. для дешифрации #FE можно проверять A0=0, A1=1 и A2=1. В разделении дешифрации смысла нет, только лишняя нагрузка на шину адреса процессора.

Сообщение отредактировал Northwood - Воскресенье, 27.09.2020, 11:11 |

| |

|

|

|