|

Pentagon by Northwood

|

|

| Black_Cat | Дата: Среда, 01.07.2020, 16:12 | Сообщение # 1 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

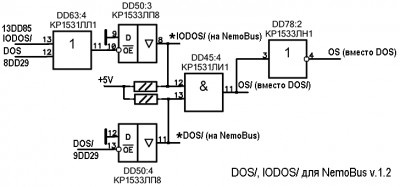

| 1. Сигналы DOS/, IODOS/ для NemoBus v.1.2

Цепи DOS/, DOS на выходе DD29 идущие на дешифрацию портов разорвать, и в разрыв врезать схему. Цепи, идущие на выборку ПЗУ оставить как есть.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Black_Cat | Дата: Воскресенье, 06.09.2020, 21:00 | Сообщение # 141 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Цитата Northwood (  ) хотя тоже самое можно сделать и через D0 #FF37

Я же объяснял, что триггер нужен, чтоб зафиксировать, что это именно режим ядра. Что NMI пришло от нужной кнопки вызова ядра, и должно обрабатываться ПЗУ ядра, а не тысячей других ПЗУ, включаемых ловушками #66, аналогично и сброс - что он пришёл от кнопки сброса, а не от RST0. Но спасибо за вопрос, т.к. против этих ловушек #00 и #66 надо будет продумать блокировку на периферию в режиме ядра :) . Т.е. в схему адаптера divIDE придётся добавить ещё одну микруху для блокировки M1/ по IODOS/ or DOS/ = 0 :)

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Воскресенье, 06.09.2020, 21:42 | Сообщение # 142 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Пока что такой вариант схемы. Добавлено (06.09.2020, 21:50)

---------------------------------------------

Цитата Black_Cat (  ) Я же объяснял, что триггер нужен, чтоб зафиксировать, что это именно режим ядра.

Ну так при нажатии на NMI, ROM_SP станет = 0, значит включится ПЗУ BIOS (ядра),

Цитата Black_Cat (  )

Что NMI пришло от нужной кнопки вызова ядра,

У нас всего одна кнопка NMI.

Цитата Black_Cat (  )

и должно обрабатываться ПЗУ ядра, а не тысячей других ПЗУ, включаемых ловушками #66,

Раз включилось ПЗУ BIOS (ядра), то будет выполняться обработчик NMI ядра.

Цитата Black_Cat (  )

аналогично и сброс - что он пришёл от кнопки сброса, а не от RST0.

Ну так RST0 не меняет состояние портов и триггеров, а по кнопке сброса порт #FF37 так же сбрасывается, как и все остальные, а значит ROM_SP станет = 0 и начнёт выполняться код BIOS (ядра).Добавлено (07.09.2020, 11:55)

---------------------------------------------

Цитата Northwood (  ) P.s. я только сделал маленькое изменение в твою схему формирования сигнала DOS - ЛИ1 заменил на ЛП5, поменяв местами DOS и DOS/. Для того, чтобы во время работы работы BIOS (POST, Setup), когда на шине будет DOS/ = IODOS/ = 0, чтобы тем самым не открывался доступ к портам TR-DOS, т.к. BIOS тогда не сможет протестировать порты атрибутов и джойстика.

Вернул как было, т.к. понял, что в режиме "ядра" доступ к FDI тоже понадобится в будущем, чтобы можно было прочитать с дискеты прошивку ПЗУ и прошить её или сохранить на дискете текущую прошивку. Просто теперь для тестирования джойстика и порта атрибутов придётся процедуру копировать в ОЗУ и запускать оттуда, где нужно будет выключить ПЗУ BIOS, сняв с шины сигналы IODOS/ и DOS/ и провести тест. После смогу назад включить ПЗУ BIOS, это снова включит на шине сигналы IODOS/ = DOS/ = 0.

|

| |

| |

| Black_Cat | Дата: Понедельник, 07.09.2020, 19:41 | Сообщение # 143 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Цитата Northwood (  ) Вернул как было, т.к. понял, что в режиме "ядра" доступ к FDI тоже понадобится в будущем, чтобы можно было прочитать с дискеты прошивку ПЗУ и прошить её или сохранить на дискете текущую прошивку. Просто теперь для тестирования джойстика и порта атрибутов придётся процедуру копировать в ОЗУ и запускать оттуда, где нужно будет выключить ПЗУ BIOS, сняв с шины сигналы IODOS/ и DOS/ и провести тест. После смогу назад включить ПЗУ BIOS, это снова включит на шине сигналы IODOS/ = DOS/ = 0.

:) Ты там ещё с кем-то чатишься? :) . Я решу этот вопрос, шоб в ядре был доступ ко всем портам .

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 00:37 | Сообщение # 144 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Нет, ни с кем пока не общаюсь по данному проекту. Последнюю неделю был очень занят, сейчас потихоньку занимаюсь оптимизацией компановки логических элементов в схеме. Есть желание выкинуть с платы хотя бы 2 корпуса микросхем.

На данный момент управление памятью работает следующим образом:

В обычном режиме, когда включено основное ПЗУ, порт управления маской #FC37 недоступен никому. Заданная ранее маска при этом действует. Замаскированные биты портов расширения памяти тоже никому недоступны в стандартном режиме, эти биты при этом тоже действуют, определяя расположение в памяти задачи и адресуя на неё экран.

При нажатии кнопки Magic происходит сброс порта управления ПЗУ #FF37, что приводит к включению ПЗУ BIOS и к разблокировка порта маски #FC37. Замаскированные биты расширения памяти по-прежнему не доступны. Обработчик по адресу #0066 должен снять маску, записав #00 в порт #FC37 - это откроет доступ ко всей памяти и переключит экраны на стандартную область - на 5 и 7 страницы относительно всех 4х МБ. По окончании взаимодействия с пользователем, когда он либо переключился на другую задачу либо создал новую в новой области ОЗУ, ядро включает выбранную область ОЗУ, используя любой из доступных портов расширения, используя менеджер памяти, затем включает нужную маску для новой задачи, тем самым заблокировав замаскированные биты расширения памяти и завершает свою работу, выключив ПЗУ BIOS, тем самым заблокировав порт маски #FC37, и возвращает управление задаче, если это было переключение на ранее созданную задачу, либо выполняет RST 0, если это новая задача.

|

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 20:43 | Сообщение # 145 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Цитата Northwood (  ) это откроет доступ ко всей памяти и переключит экраны на стандартную область - на 5 и 7 страницы относительно всех 4х МБ

Т.е. младшие 8 страниц - это всегда АВМ ядра? Жирновато для ядра..

И такой вопрос на засыпку по джойстику - это предполагается чото самопальное с ручкой и 4мя кнопками? Т.к. серийного с 4мя кнопками я чото не знаю. Да и для Kempston нет прог поддерживающих более 3х кнопок, да и те можно сосчитать на пальцах. В чём тогда смысл 4й кнопки? Кстати, по D6=0 проги определяют наличие джоя. Да и цоколёвка ни в какой стандарт не лезет.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 20:59 | Сообщение # 146 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) Т.е. младшие 8 страниц - это всегда АВМ ядра? Жирновато для ядра..

Этого много, но мы память будем бить минимум по 128 КБ, более мелкого дробления не будет, поэтому последние 128 КБ в многозадачном режиме всё равно по-другому использовать не получится.

Цитата Black_Cat (  )

И такой вопрос на засыпку по джойстику - это предполагается чото самопальное с ручкой и 4 кнопками? Т.к. серийного с 4мя кнопками я чото не знаю. Да и для Kempston, нет прог поддерживающих более 3х кнопок, да и их можно сосчитать на пальцах. В чём тогда смысл 4й кнопки?

ШД у нас 8 бит, свободные входы у КП11 тоже есть, развести лишнюю дорожку не сложно, пусть будет. Или ты хотел вместо 4-й кнопки что-то другое сделать ?

|

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 21:12 | Сообщение # 147 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Цитата Northwood (  ) ШД у нас 8 бит, свободные входы у КП11 тоже есть, развести лишнюю дорожку не сложно, пусть будет. Или ты хотел вместо 4-й кнопки что-то другое сделать ?

Ну, щаз в качестве джоев к Спекам юзают обычно Sega Genesis/Mega Drive, а там без усложнения схемы токо 2 кнопки, и обратная с Кемпстоном полярность, не говоря уже о цоколёвке.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 21:12 | Сообщение # 148 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| На счёт блокировки порта #FC37 в стандартном режиме, оказывается я её хотел сделать, но забыл. Теперь сделал на DD61:2.

Так же добавил чтение порта #EFF7 - 5 бит (из них 4 - управление видеорежимами и 1 - RAMROM). Оставшимися 3 битами буду читать состояние бордюра #FE.

Новую микросхему КР1533ИР22 для чтения #EFF7 и #FE едва смог запихнуть на плату.

|

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 21:28 | Сообщение # 149 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

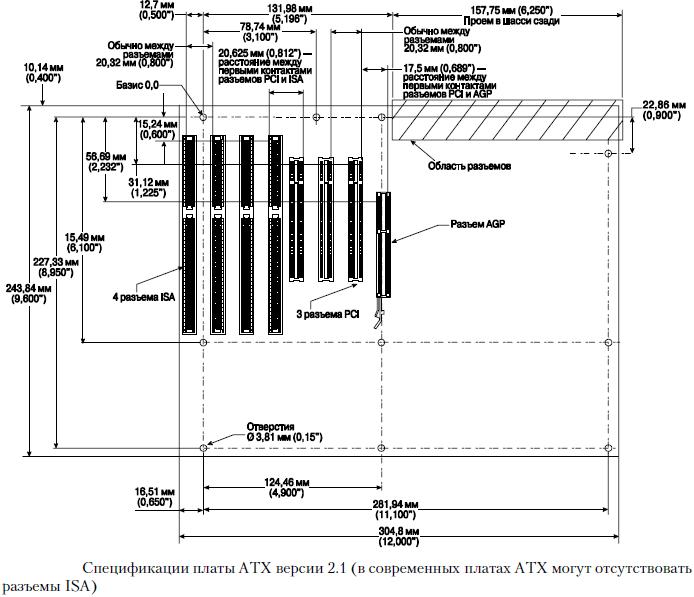

| Чото у тя о5 с расположением слотов не то - на глаз же видно. ISA слот полюбому должен либо быть впритык к NemoBus, на половинном расстоянии, либо на полуторном расстоянии. И если бы ты поставил ISA как я предлагал между двумя верхними слотами, то можно было бы сэкономить место целого слота, или добавить краевой разъём.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 21:33 | Сообщение # 150 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| ISA чётко по документации расположен. Он почти на самом краю платы ATX.

|

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 21:37 | Сообщение # 151 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Цитата Northwood (  ) ISA чётко по документации расположен. Он почти на самом краю платы ATX.

Не знаю чо там за документация, но расстояние между серединами ближайших слотов ISA и NemoBus должно быть либо 1 см, либо 3 см, а у тебя я этого не вижу. И если твой стандарт верный, то значит все NemoBus неправильно стоят, и их нужно сдвинуть ниже.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 21:47 | Сообщение # 152 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) Не знаю чо там за документация, но расстояние между серединами ближайших слотов ISA и NemoBus должно быть либо 1 см, либо 3 см, а у тебя я этого не вижу.

https://www.google.com/search?....nz1y3ZM

Цитата Black_Cat (  ) И если твой стандарт верный, то значит все NemoBus неправильно стоят.

Дык, по твоим размерам делал.

|

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 22:06 | Сообщение # 153 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Цитата Northwood (  ) https://www.google.com/search?....nz1y3ZM

Ну вот какое расстояние между ISA и PCI, такое же должно быть и до NemoBus. На глаз же видно. Ищи ошибку, или давай пикад псб, бум искать вместе :) . Расстояние между ближайшими рядами контактов ISA и NemoBus должно быть 5,08 мм.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 22:21 | Сообщение # 154 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| По этому рисунку как раз всё правильно и выходит. Расстояние между верхним рядом ножек PCI и нижним рядом ножек ISA указано 0.812", у меня 0.800", эти 0.012" мелочь, учитывая что в PCI 4 ряда контактов, а не 2. Ну а визуально чертёж этот не точный, линии нарисованы приблизительно, плюс / минус лапоть.

Вообще я находил множество разных чертежей платы ATX, везде есть отличия.

Сообщение отредактировал Northwood - Пятница, 11.09.2020, 22:25 |

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 22:28 | Сообщение # 155 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Цитата Northwood (  ) Расстояние между верхним рядом ножек PCI и нижним рядом ножек ISA указано 0.812", у меня 0.800"

Забудь про PCI, у тя везде SL62. Давай пикад, я сам найду.Добавлено (11.09.2020, 22:32)

---------------------------------------------

Цитата Northwood (  ) Вообще я находил множество разных чертежей платы ATX, везде есть отличия.

:) Отличия, отличиям - рознь!

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 22:35 | Сообщение # 156 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Держи PCB файл.

Толщина разъёмов ISA и PCI отличается не на столько сильно, чтобы всё получалось точно как на том рисунке визуально.

|

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 22:52 | Сообщение # 157 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Кароче, меряем от базиса 0,0 - у тя ISA смещена вниз на 5,08 мм, исправляй.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 23:03 | Сообщение # 158 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Цитата Black_Cat (  ) Кароче, меряем от базиса 0,0 - у тя ISA смещена вниз на 5,08 мм, исправляй.

Тогда не сходится размер на чертеже - "Расстояние между первыми контактами ISA и PCI", должно быть 812 миль, у меня было 800 миль, стало 600 миль.

Добавлено (11.09.2020, 23:08)

---------------------------------------------

Вот нашёл другой чертёж, кстати, именно по нему я и расстанавливал элементы. Там уже другая картина.

http://perscom.ru/system-plates/44-form-factori/start5

Разница между первым и вторым чертежом в том, что на первом расстояние 500 миль указано между базисом 0,0 и нижним рядом 2-го слота ISA. А на втором это же расстояние 500 миль указано между базисом 0,0 и нижним рядом 1-го слота ISA. Т.к. слоты идут с шагом 800 миль, то вот эта разница между чертежами и даёт не соответствие в 200 миль (5.08 мм).

2-му чертежу я верю больше, т.к. на 1-м есть противоречия.

Сообщение отредактировал Northwood - Пятница, 11.09.2020, 23:16 |

| |

| |

| Black_Cat | Дата: Пятница, 11.09.2020, 23:17 | Сообщение # 159 |

Координатор

Группа: Координаторы

Сообщений: 737

Статус: Offline

| Две картинки - два разных расстояния от базиса 0,0 отличающихся на 5,08 мм. И какая правильная?

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

| |

| Northwood | Дата: Пятница, 11.09.2020, 23:19 | Сообщение # 160 |

80h

Группа: Пользователи

Сообщений: 131

Статус: Offline

| Я верю 2-му чертежу, потому что на 1-м как не расставляй слоты, что-то в размерах да не сходится. Либо расстояние между базисом, либо расстояние между ISA и PCI. А на 2-м чертеже всё сошлось.

|

| |

| |

|