|

ZXEvo - программные и аппаратные и доработки

|

|

| Black_Cat | Дата: Пятница, 12.07.2013, 14:47 | Сообщение # 1 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

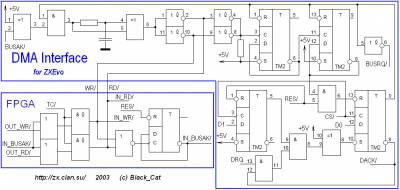

| 1.0 DMA Interface for ZXEvo.

В ZXEvo нет штатной возможности использования внутреннего контроллера ПДП для работы с устройствами в слотах, т.к. на FPGA не заведены сигналы BUSRQ/ и BUSAK/. Этот недостаток можно обойти, оснастив внешнее устройство специальным DMA интерфейсом, программно запускающим и автоматически останавливающим процесс ПДП. Ниже представлена схема такого интерфейса.

Данный интерфейс позволяет использовать внутренний контроллер ПДП в трёх режимах работы:

1) немедленная одиночная операция с данными (байтом, или блоком данных);

Операция с данными производится сразу же после прихода BUSAK/.

2) отложенная продолженная операция с данными активируемая по внешнему вызову;

Однотипная операция с данными производится многократно по мере поступленя внешнего вызова. Режим выключается программно.

3) немедленная продолженная операция с данными активируемая по внешнему вызову;

Однотипная операция с данными производится многократно по мере поступленя внешнего вызова, но первая операция производится сразу после прихода BUSAK/. Режим выключается программно.

Принцип действия.

Внешний порт управления, выбираемый сигналом CS/, устанавливает разрядами D0, D1 выбранный режим и формирует запрос ПДП. При получении подтверждения BUSAK/, линии RD/, WR/ одновременно кратковременно устанавливаются в ноль при единице на линиях MREQ/ и IORQ/, что фиксируется счётчиками ПДП интерфейса и FPGA, при этом последний вырабатывает сигнал IN_BUSAK/, запускающий внутренний цикл ПДП. По окончании цикла ПДП вырабатывается сигнал TC/ (Terminal Count), повторно кратковременно устанавливающий линии RD/, WR/ одновременно в ноль. Это сбрасывает внутренний счётчик и прекращает сигнал IN_BUSAK/. Одновременно внешний счётчик сбрасывает триггер разряда D0 порта управления и снимает BUSRQ/, завершая цикл ПДП. Соответствие режима разрядам DO, D1 приведено ниже:

D1D0

0 0 - неактивное состояние;

0 1 - 1 режим;

1 0 - 2 режим;

1 1 - 3 режим.

В режимах 2 и 3 сигнал запроса ПДП DRQ формируется внешним устройством, которое может по RD/=WR/=0 выставлять ноль на разряд шины данных, соответствующий выделенному ему ПДП каналу, и снимать его после установки RD/=WR/=1. Если устройство не выставляет номер канала, то по умолчанию всегда используется ПДП канал 7. Всего поддерживается 7 каналов, ниже приведено соответствие каналов и разрядов шины данных:

0-3 - зарезервировано под 4х канальную звукову карту (аналог DMAUSC);

4 - 0 - внешний контроллер ПДП, 1 - внутренний контроллер ПДП;

5 - зарезервировано под ISA Sound Blaster;

6 - зарезервировано под ISA Ethernet;

7 - зарезервировано под NemoBus.

Приоритет каналов уменьшается с увеличением номера. Внешний контроллер ПДП программно аналогичен IBM PC.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Black_Cat | Дата: Понедельник, 15.07.2013, 06:46 | Сообщение # 2 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

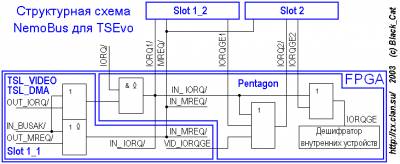

| 2.0 NemoBus for TSEvo.

Ниже приведена структурная схема реализации NemoBus для TSEvo. Функционально, одна часть FPGA относится к TSLVideo Card, а вторая собственно к компьютеру Pentagon. Структурно TSLVideo Card и Slot1 работают параллельно. Такое включение не является чем-то особеным, ибо такая возможность изначально заложена в NemoBus в виде дублирующего игольчатого разъёма на NemoBus картах. При таком включении, сигналы IORQGE реальных параллельных карт объединяются как монтажное ИЛИ. Функционально, к TSLVideo Card помимо собственно видеокарты так же отнесены TSLDMA и ZSD, при том последняя только для того, что бы исключить конфликты с SounDrive v.1.52, которую можно вставить в Slot2. В соответствии с функциональным разделением в FPGA, так же должны быть отделены и дешифраторы TSLVideo Card и Pentagon.

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|

| Yuri | Дата: Понедельник, 20.01.2014, 17:29 | Сообщение # 3 |

|

08h

Группа: Пользователи

Сообщений: 12

Статус: Offline

| Я вот всё хотел спросить - какое максимальное разрешение в граф режиме для TS EVO? Как там TS Labs сражается?

|

| |

|

|

| Black_Cat | Дата: Среда, 22.01.2014, 10:26 | Сообщение # 4 |

Координатор

Группа: Координаторы

Сообщений: 739

Статус: Offline

| Цитата Yuri (  ) какое максимальное разрешение в граф режиме для TS EVO? Как там TS Labs сражается?

360x288, доки здесь: http://tslabs.info/forum/viewtopic.php?f=35&t=157

"Трудно найти чёрную кошку в тёмной комнате.. ...особенно, если её там нет", "Forever!".

"Я никогда не причиняю им зла. Я говорю им правду, и они думают, что это - зло."

Гарри Трумэн

|

| |

|

|