|

ИHТЕРФЕЙС ЖЕСТКОГО ДИСКА IDE

|

|

| Hazar | Дата: Суббота, 05.03.2016, 20:03 | Сообщение # 1 |

80h

Группа: Пользователи

Сообщений: 231

Статус: Offline

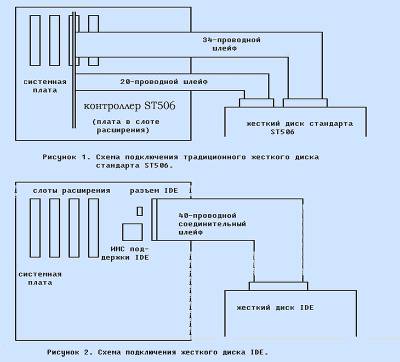

| Интерфейс, используемый для подключения жестких дисков и других накопителей к компьютерам, обычно называют IDE (Integrated Drive Electronics —

встроенный интерфейс накопителей); однако более правильно называть этот интерфейс следует как ATA (AT Attachment) Интерфейс был предназначен для подключения

комбинации накопителя и контроллера к 16 разрядной шине компьютера IBM AT ( 1984 г.) Шина AT больше известна как ISA (Industry Standard Architecture— архитектура шины

промышленного стандарта). Официально интерфейс называется ATA, но производители оборудования используют маркетинговое название интерфейса как “IDE”

Integrated Drive Electronics . Что говорит о том, что электроника интерфейса или контроллера встроена в накопитель, а не расположена на отдельной плате, как в

устройствах предыдущих поколений.

История развития интерфейса IDE

За время существования ПК было разработано несколько интерфейсов

ST 506/412 1978 -- 1989 годы (устарел)

ESDI 1983 1991 годы (устарел)

IDE (не ATA) 1987–1993 годы (устарел)

SCSI С 1986 года по настоящее время IDE

(Parallel ATA) С 1986 года по настоящее время

Serial ATA С 2003 года по настоящее время

Добавлено (05.03.2016, 19:41)

---------------------------------------------

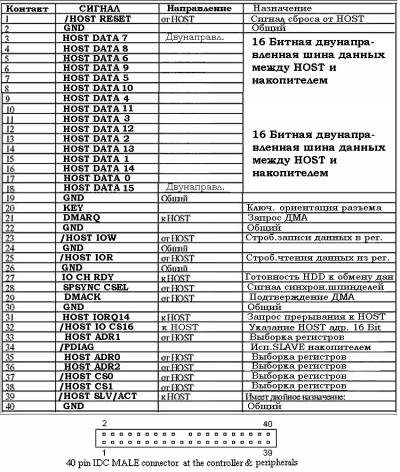

Описание сигналов интерфейса В стандарте АТА обмен между контроллером и накопителем, а также передаваемые

по нему команды производится через регистры .Интерфейс имеет 8 регистров, занимающих 8 адресов в пространстве

ввода-вывода. Ширина шины данных составляет 16 бит. Количество каналов, присутствующих в системе, может быть больше 2.

Главное, чтобы адреса каналов не пересекались с адресами других устройств ввода-вывода. К каждому каналу можно

подключить 2 устройства (master и slave), но в каждый момент времени может работать лишь одно устройство.

Физически интерфейс IDE реализован при помощи плоского 40- или 80-жильного кабеля, на котором могут быть разъемы для

подключения одного или двух устройств. Общая длина кабеля не должна

превышать 45 см, причем между разъемами должно

быть расстояние не менее 15 см. Все сигналы интерфейса являются логическими с уровнями ТТЛ

Добавлено (05.03.2016, 20:01)

---------------------------------------------

IDE - это интерфейс логического уровня, а не прямого управления “железного” уровня устройства. Диски IDE принимают высокоуровневые команды,

такие как форматирование дорожки или чтение сектора, электрическое соединение обеспечивает обмен командами и данными

между управляющей системой и дисками 8- или 16-битовыми порциями. Электрический

интерфейс IDE сам по себе простой, а вся значимая функциональная электроника расположена в накопителе.

Добавлено (05.03.2016, 20:03)

---------------------------------------------

Spectrum жив в нашей душе навсегда

Сообщение отредактировал Hazar - Воскресенье, 06.03.2016, 12:03 |

| |

|

|

| Hazar | Дата: Суббота, 05.03.2016, 20:40 | Сообщение # 2 |

80h

Группа: Пользователи

Сообщений: 231

Статус: Offline

| Параллельный интерфейс ATA представляет собой шину, в которой все сигналы соответствуют стандартной логике ТТЛ:♦

высокий уровень выходного сигнала не ниже 2,4 В (при токе до 400 мкА, сигнал DMARQ— до 500мкА), низкий уровень не выше 0,5 В

(при токе 4 мА, для линии 39 DASP (SLV...) ради совместимости со старыми устройствами — 12 мА);♦ высокий уровень входного сигнала не ниже 2,0 В,

низкий уровень не выше 0,8 В. допустимая емкость проводников — не более 35пФ. Терминаторы стандартом не предусматриваются

(они имеются в каждом устройстве и хост-адаптере),

Здесь приведены обозначения из стандарта ATA/ATAPI- 4.♦

RESET#(DeviceReset) — сброс устройства (инвертированный сигнал сброса системной шины). Сигнал

длительностью не менее 25 мкс вырабатывается после

установления питающих напряжений. Сигнал вызывает сброс интерфейса в исходное состояние и устанавливает параметры по умолчанию.♦

DA[2:0] (DeviceAddress) — три младших бита системной шины адреса, используемые для выбора регистров устройств.♦

DD[15:0] (DeviceData) — двунаправленная 16-битная шина данных между адаптером и

устройствами. При 8-битных обменах используются младшие биты D[7:0].

У устройства не должно быть «подтягивающего» резистора на линии DD7— на

хост-контроллере эта линия через резистор 10 кОм соединена с шиной GND.

Это позволяет хосту определить факт отсутствия устройства на шине сразу

после аппаратного сброса: при чтении регистра состояния отсутствующего

устройства бит

BSY окажется сброшенным.♦

DIOR#(Device I/ORead) — строб чтения портов ввода-вывода. Данные фиксируются по

положительному перепаду сигнала.♦

DIOW# (Device I/OWrite) — строб записи портов ввода-вывода. Данные фиксируются по

положительному перепаду сигнала.♦

IORDY (I/O channelReady) — готовность устройства завершить цикл обмена.

Низким уровнем сигнала во время цикла обмена устройство может ввести

такты ожидания шины.

Сигнал требуется при обмене в PIO Mode 3 и выше. На хост-контроллере эта линия через резистор 1 кОм должна подтягиваться

к шине питания.♦

IOCS16#— разрешение16-битных операций. Обращение ко всем регистрам, кроме регистра данных, всегда 8-битное. Для

PIO Mode 0, 1, 2 при активном сигнале

обращения 16-битные, при неактивном — 8-битные. Для PIO Mode 3, 4 и DMA все обмены 16-битные, кроме дополнительных байтов

(выходящих за границу 512-байтного сектора) «длинного» считывания и записи. Начиная с ATA/ATAPI-3 не используется.♦

DMARQ (DMARequest) — запрос обмена по каналу DMA (необязательный). При

разрешении обмена сигнал (высокий уровень) вводится устройством по

готовности к обмену.

Введя сигнал DMARQ, устройство должно дождаться подтверждения от хост-адаптера сигналом DMACK#, после чегоможет снять

запрос DMARQ. Для очередной

передачи запрос должен быть введен снова. В режиме Multiword DMA запрос может удерживаться на время передачи всех

данных. Выход должен быть тристабильным, во

время работы с DMA он может быть в активном состоянии (0 или 1) только у выбранного

устройства. В ATA-1 для этого сигнала мог использоваться как

тристабильный, так и стандартный ТТЛ-выход. Работа на одной шине устройств с

разнотипными выходами DMARQможетпривести к конфликтам. На

хост-контроллере

линия должна соединяться с шиной GND через резистор 5,6 кОм.♦

DMACK#(DMA Acknowledge) — подтверждение DMA. Сигнал вырабатывается хост-адаптером

как подтверждение цикла передачи. Передача слова

данных управляется сигналами DIOR#или DIOW#. Во время обмена по каналу DMA сигналы IOCS16#,

CS0#и CS1# не используются, обмен всегда производится 16-битными

словами.♦

INTRQ (Interrupt Request) — запрос прерывания. Выход должен быть тристабильным, активный сигнал (логическую единицу)

вырабатывает только

выбранное устройство, когда у него имеется необслуженный запрос прерывания и его вырабатывание не запрещено битом

nIENв регистре Device Control.

Запрос сбрасывается по сигналу RESET#, установке бита SRSTв регистре DeviсеControl, записи врегистр команд или

чтении регистра состояния. При обменах

PIO запрос устанавливается в начале передачи каждого блока (сектора или группы секторов при

многосекторных операциях). Исключения: по командам

Format Track, Write Sector(S), Write Buffer и Write Long в началепередачи первого

блока данных запрос прерывания не вырабатывается. При обменах

DMA запрос прерывания вырабатывается только по завершении операции. На

хост-контроллере эта линия через резистор 10 кОм должна подтягиваться к шине GND.♦

CS0#(Chip Select0) — сигнал выбора блока командных регистров

(Command Block Registers). Для первого канала он вырабатывается при наличии на системной шине адреса порта

ввода-вывода в диапазоне 1F0h-1F7h (сигнал так же называют CS1FX#).♦

CS1#(Chip Select1) — выбор блока управляющих регистров (Control Block Registers). Для

первого канала он вырабатывается при наличии на системной шине адреса порта

ввода-вывода в диапазоне 3F6h-3F7h (часто этот сигнал называется CS3FX#).♦

PDIAG#(PassedDiagnostics) — сигнал о прохождении диагностики. Ведущее устройство наблюдает за этим сигналом,

который ведомое устройство должно выработать в ответ на сброс или команду диагностики. Если ведомое устройство обнаружено

(по сигналу DASP#), ведущееустройство ожидает сигнал в течение 31 с после сброса и 6 с после команды диагностики.

Если за это время сигнал не появился, ведущее устройство отмечает этот факт

установкой бита 7 регистра ошибок. Если ведомое устройство не

обнаружено, ведущее обнуляет регистр состояния ведомого устройства и сообщает свое

состояние сразу после завершения собственной самодиагностики. Сигнал

служит только для связи двух устройств и хост-адаптером не используется (в ATA-4 контакт задействован для сигнала CBLID#).♦

CBLID#(Cable assembly type identifier) — идентификация типа кабеля. В 80-проводной

сборке контакт 34 наразъеме хост-адаптера соединяется с шиной GND, а

контакты34 разъемов устройств соединяются между собой, но связи с

разъемом

хост-адаптера не имеют. На устройстве эта линия через резистор 10 кОм должна

подтягиваться к шине питания. После прохождения сброса (когда сигнал

PDIAG#снимается)хост может определить наличие 80-проводного кабеля по

низкому уровню сигнала.♦

DASP#(DeviceActive, Slave Present) — сигнал двойного назначения: индикатор активности устройства и

присутствия ведомого устройства.

Устройства имеют выход типа «открытый коллектор» с нагрузочным резистором 10 кОм к шине +5 В. После сброса

по сигналу RESET#или при инициализациипо включении питания оба устройства в течение 1 мс должны деактивировать этот

сигнал, после чего не позже чем через 400 мс его вводит ведомое устройство для сообщения о своем присутствии. Ведущее

устройство не активирует этот сигнал в течение 450 мс. Сигнал деактивируется

ведомым устройством после получения им команды или через 31 с

автоматически (смотря что произойдет раньше). После этого сигнал может быть введен любым устройством как индикатор активности.

Адаптер использует этот сигнал для включения светодиодного индикатора доступа к диску.

Добавлено (05.03.2016, 20:13)

---------------------------------------------

Адресные сигналы активны в диапазонах портов ввода/вывода 1F0-1F7 и 3F0-3F7. Управляющие регистры контроллера флоппи-дисков также находятся вдиапазоне 3F0-3F7,

но не присутствуют на диске IDE.

Таблица 2: Определение регистров жесткого диска.

сигнал выбора CS1,CS3 активен в диапазонах адресов ввода/вывода 1F0-1F7 и 3F0-3F7.

Адрес ввода/вывода Регистр для чтения записи HEX

1F0 Data register Data register Жесткий

1F1 Error register Write precomp Жесткий

1F2 Sector count Sector Count Жесткий

1F3 Sector number Sector number Жесткий

1F4 Cylinder low Cylinder low Жесткий

1F5 Cylinder high Cylinder high Жесткий

1F6 Drive/head Drive/head Жесткий

1F7 Status register Command register Жесткий

3F6 - Fixed disk Жесткий

1F0 Регистр данных Регистр данных

1F1 Регистр ошибок Регистр предкомпенсации

1F2 Регистр счетчика секторов Регистр счетчикасекторов

1F3 Регистр номера сектора Регистр номера сектора

1F4 Регистр номера цилиндра мл. Регистр номера цилиндра мл.

1F5 Регистр номера цилиндра ст. Регистр номера цилиндра ст.

1F6 Регистр накопителя/головки Регистр накопителя/головки

1F7 Регистр состояния Регистр команд

3F6 Регистр альтернативного сост. Состояние накопителя

3F7 Регистр адреса накопителя Не используется

Принцип адресации CHS заложен в названии. Сперва блок головок устанавливается позиционером на требуемую дорожку (Cylinder), после этого

выбирается требуемая головка (Head), а затем считывается информация из требуемого сектора (Sector).

Spectrum жив в нашей душе навсегда

Сообщение отредактировал Hazar - Суббота, 05.03.2016, 20:58 |

| |

|

|

| Hazar | Дата: Суббота, 05.03.2016, 23:52 | Сообщение # 3 |

80h

Группа: Пользователи

Сообщений: 231

Статус: Offline

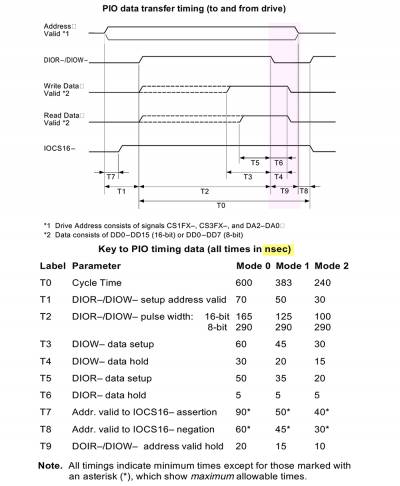

| Временные диаграммы передачи данных

Spectrum жив в нашей душе навсегда

|

| |

|

|

|