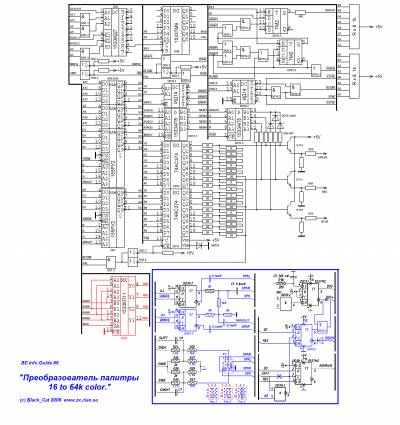

Преобразователь палитры 16 to 64k color. Описание схемы.

Предназначена для преобразования существующей цветовой палитры компьютера в произвольную в рамках палитры из 64k цветов.

Схема состоит из ОЗУ палитры на DD4-DD7, ЦАПов на DD12, DD13, дешифраторов портов на DD3, DD10.1, порта управления #3FFF на DD8, порта адреса на DD16.1, селектора режима записи на DD16.2, и коммутатора видеосигнала на DD11.2, DD1.4, DD2.3, DD2.4. Кроме того схема содержит дополнительные узлы предназначенные исключительно для Pentagon-1024SL v2.2, это декодер синхросигналов на DD10.2 (является необязательным и может быть исключён), и коммутатор входных сигналов, предназначенный для высвобождения ног ПЛИС EPM7128 на DD11.1. Схема так же содержит попутные доработки выделенные цветом. Красная доработка позволяет задавать цвет пикселей в режиме 16color полубайтами, что значительно упрощает их обсчёт и позволяет в целом ускорить обработку графики за счёт её оптимизации. Синие доработки увеличивают функциональность звукового воспроизведения через бипер, добавляя возможность стереовоспроизведения, а так же двухбитного моно воспроизведения, а так же добавляется возможность доступа в произвольный момент к портам DOS путём активации сигнала IODOS/.

Принцип действия преобразователя палитры.

Преобразователь палитры может работать в двух режимах записи данных в ОЗУ палитры - 16ти и 12ти разрядном режимах записи. Соответственно, в этих режимах обновляются данные либо для всего цветового диапазона 64k, либо только для 4k цветов из 64k. Так же, эти режимы записи требуют разное количество обращений к портам - соответственно 32 обращения или 16 обращений, а потому дают программисту дополнительную возможность более гибкого расходования машинного времени. В 16ти разрядном режиме записи сначала в порт #xxF6 записывается 4х разрядный адрес, затем в порт #xx7E записываются 16 разрядные данные, при том старшим байтом данных является старший байт адреса этого адресного диапазона портов. В 12ти разрядном режиме записи данные и адрес записываются сразу в порт #xx7E, при этом D0-D3 задают адрес ячейки памяти, а D4-D7 и A8-A15 являются записываемыми данными. Структура данных в 16ти разрядном режиме: старший разряд -> G3G2G1G0R3R2R1R0 B3B2B1B0G5G4R4B4 <- младший разряд. Структура данных в 12ти разрядном режиме: старший разряд -> G3G2G1G0R3R2R1R0 B3B2B1B0A3A2A1A0 <- младший разряд.

Для определения в каком режиме производится запись в ОЗУ служит селектор режима записи на DD16.2, который распознаёт режим записи в зависимости от того к какому порту было первое обращение. Если к #xxF6, то это 16ти разрядный режим, если к #xx7E - то соответственно 12ти разрядный режим записи. При программировании необходимо иметь ввиду, что в 12ти разрядном режиме записи на адресных входах ОЗУ будет присутствовать не текущий записанный адрес, а предыдущий. Это обусловлено тем, что адрес на адресные входы ОЗУ поступает не непосредственно, а через конвейерную запись с задержкой на один цикл записи. Поэтому в 16ти разрядном режиме адрес приходит к ОЗУ одновременно с данными, а в 12ти разрядном режиме - запаздывает на один цикл записи. Поэтому при работе в 12ти разрядном режиме записи важно знать какой адрес присутствует на ОЗУ в начальный момент. Кроме того необходимо иметь ввиду, что старший разряд адреса A4 одновременно является яркостным разрядом BRIGHT в цвете бордюра. Т.е. какой последний адрес оставался на адресном конвейере, таким и будет в дальнейшем отображаться бордюр. Поэтому при программировании, чтоб не делать лишних циклов записи, последним на адресный конвейер кладётся тот адрес, который будет первым при следующем программировании палитры.

Режим отображения палитры включается сигналом PAL=1, записью D7=1 #3FFF. Запись в ОЗУ возможна только при активном сигнале BLANK/, т.е. только во время обратного хода луча развёртки телевизора. При записи в порты #xxF6 или #xx7E во время отображения экрана или бордюра, соответственно будет меняться цвет бордюра, при том во всех 15 цветах доступных Спектруму. При записи в порт #xxFE будут меняться только RGB составляющие цвета бордюра.

На DD10.2 для Pentagon-1024SL v2.2 реализован декодер синхросигналов. Основное его назначение - экономия выводов ПЛИС, т.к. позволяет через две ноги вывести четыре синхросигнала. В случае, если такая экономия, или такие сигналы не нужны, этот узел может быть исключён.

На DD11.1 реализован коммутатор входных сигналов ПЛИС EPM7128. Его назначение - высвобождение ног ПЛИС для организации вывода через одну из них сигнала BLANK/. Основанием для такого уплотнения служит то, что выводы MEM1-MEM4 используются только при обращении процессора к памяти, а сигналы PORT1-2 и IORQG только при обращении к портам, а т.к. процессор не может одновременно обращаться и к памяти и к портам, то эти сигналы можно пропускать через одни и те же выводы ПЛИС в разное время. Для этого соответствующие выводы ПЛИС должны быть перепрограммированы на режим ОК с внутренним пуллапом, а внутренние сигналы MEM1-MEM4 подаваться на выход через элементы ИЛИ стробируемые сигналом MEMRQ/. Соответственно сигналы PORT1-2 и IORQG от выводов ПЛИС внутрь тоже должны поступать через элементы ИЛИ стробируемые инверсным сигналом MEMRQ. При этом необходимо изменить кодирование сигналов PORT1-2 так, чтоб неактивному состоянию соответствовало высокое значение этих сигналов.

Перспективы развития преобразователя палитры.

Конструкция имеет открытую архитектуру и без всяких изменений в управлении может быть масштабирована для отображения 256 или 4k цветов из палитры 64k (при соответствующем увеличении объёма ОЗУ и разрядности порта адреса).

При повторении конструкции рекомендуется всю управляющую логику выполнить на ПЛИС типа EPM3032.

Источники:

Мотивацией для разработки этой схемы послужила схемотехника преобразователя палитры компьютера Profi-3+ и разработка DDp: http://realddp.narod.ru/zx/pal444/ .

Попутные доработки:

Модификатор структуры байта видеоданных для видеорежима 16color.

Схема выполнена на мультиплексоре DD17, и при активации сигнала MOD=1, записью D6=1 #3FFF, переставляет местами биты в считываемых из видео ОЗУ данных таким образом, что данные записанные в удобном для программирования полубайтном формате IGRBigrb корректно воспроизводятся в видеорежиме изначально рассчитанном на формат представления видеоданных IiGRBgrb. При этом чётным пикселам соответствует младший полубайт D0-D3 (igrb), а нечётным пикселам соответствует старший полубайт D4-D7 (IGRB). Выделение видеоданных для пикселов в полубайты значительно упрощает их обсчёт и позволяет в целом ускорить обработку графики за счёт оптимизации её обработки.

Конструктивно мультиплексор врезается между ОЗУ и ПЛИС, таким образом, что бы данные читаемые CPU не изменялись. Сигналы на ПЛИС RAM0-RAM3 заменяются на RM0-RM3 согласно схеме.

Порт открытия доступа к теневым портам TR-DOS.

Схема реализована на DD18.2, DD15.4 и неиспользованном элементе на плате Pentagon-1024SL v2.2 DD20.2. Доступ к теневым портам открывается при записи D7=1 #EDF7 или #EFF7. Сигнал IODOS/ следует вывести на контакты B20 шины NemoBus.

Расширенный биперный вывод звука.

Схема добавляет отсутствующий в Pentagon-1024SL v2.2 выход TAPE OUT, а так же возможность вывода биперного стереозвука или монофонического двухбитного звука через D3, D4 #xxFE. Блок перемычек JP1 распаивается на макетном поле.

Коммутация спикера:

В схеме смесителя необходимо разъединить резисторы смесителя спикера R25, R31 и подключить их соответственно к контактам 2 и 11 блока перемычек.

На Рис.1 показано подключение к смесителю 2х битного монофонического выхода спикера через разделительные конденсаторы. Одновременно с контактов 4 и 7 можно снимать монофонический сигнал без разделительных конденсаторов, а с выходов 3, 6, 9, 12 можно снимать однобитный стереосигнал через разделительные конденсаторы.

На Рис.2 показано подключение к смесителю однобитного стереосигнала. Одновременно с контактов 4 и 7 можно снимать монофонический сигнал без разделительных конденсаторов, или с 1 и 4 тот же сигнал, но через разделительный конденсатор.

На Рис.3 показано подключение к смесителю на контакты 2, 5, 8, 11 внешнего стереосигнала. Одновременно с контактов 4 и 7 можно снимать монофонический сигнал без разделительных конденсаторов, или с 1 и 4 тот же сигнал, но через разделительный конденсатор, а с выходов 3, 6, 9, 12 можно снимать однобитный стереосигнал через разделительные конденсаторы.

BC Info Guide #5.

© Black_Cat 2009 www.zx.clan.su